Abstract

The interline power flow controller (IPFC) based on a modular multilevel converter with a half-bridge configuration can control the active and reactive power flows of multiple alternating current (AC) lines. However, it forms a multiterminal system on the direct current (DC) side, which leads to DC faults. To reduce the protection and clearance requirements on the DC side of IPFCs, this paper proposes a hybrid current limiter topology suitable for generating a DC-side fault ride-through scheme. The current limiter employs a low-loss branch in steady-state conditions; when the fault occurs, a commutation capacitor and controllable power electronic devices are used to transfer the fault current to the current-limiting branch. To clarify the operating principles of the current limiter, the working states of each stage and electrical stress of each device are analyzed. Different components with varying limiter parameters are also discussed, and optimal parameters to achieve the best limitation effect are discussed. PSCAD simulations show that the proposed limiter can limit the overcurrent effectively, and DC-side fault clearance can be achieved easily with this fault ride-through strategy.

Keywords: interline power flow controller; hybrid current limiter; modular multilevel converter; commutation capacitor; circuit breaker fault clearance

1. Introduction

In recent years, there has been a continuous increase in power demand, leading to a significant mismatch between the power transmission capacity of power lines and the inability of the current grid systems to meet the power demand. To address this issue, a flexible AC transmission system (FACTS) has been proposed previously. The use of power electronics and corresponding control technologies enables flexible and rapid adjustment of the impedance, voltage, and phase of AC systems, which in turn facilitates flexible control of the active and reactive power flows in lines, thus meeting the needs of power grids during operation [1]. Some scholars have also proposed adding Unified Power Quality Conditioners (UPQCs) to transmission lines to solve power quality problems for sensitive load under weak grid conditions and isolated areas or islands connected to the mainland through long submarine cables [2,3].

One of the most typical FACTSs is the unified power flow controller; however, it can only control the active and reactive power in AC lines. With the increasing amount of renewable energy, power fluctuations have become more common. Due to this, power lines suffer from overload, and this is becoming a common problem that needs to be addressed urgently. Thus, more AC lines must be controlled, and an interline power flow controller (IPFC) was proposed.

The IPFC is a new generation of FACTS that possesses powerful power flow control ability [4]. It can quickly and flexibly control the active and reactive power flows of multiple lines, thereby significantly improving the transmission efficiency [5,6,7]. Unlike series or parallel FACTS, the IPFC can have multiple converter stations, each connected by a DC bus. When a fault occurs in the DC bus, the DC current rapidly increases. If the fault current is not limited, it will cause the fault current to be too large, ultimately leading to the IPFC exiting operation.

Specifically, the converter stations of the IPFC are in series with the AC line, whereas they are connected by DC lines on the DC side; this forms a multiterminal system. Therefore, the IPFC suffers from DC faults, analogous to DC grids. It is known that due to the low inertia and low impedance characteristics of DC grids, the DC fault current and its amplitude generally increase sharply during the short-circuit fault period [8,9]. Because DC system fault currents are characterized by fast rising rates, high amplitudes, and no zero-crossing points, they are more challenging to cut off than AC fault currents. Without considering the AC-measured feed-in current, after a short-circuit fault occurs on the DC side of the modular multilevel converter (MMC), the MMC submodule can be equated to a second-order RLC circuit with a rapid increase in the capacitor discharge current and simultaneous large voltage drop. When a DC short-circuit fault causes the bridge arm current or capacitor voltage to exceed the protection threshold, the system enters a blocking state after a short delay, and the IPFC exits the operation. Here, we designed a fault current limiter (FCL) for the DC side of the IPFC. The current limiter is connected in series in the DC line of the IPFC and presents a low-impedance characteristic during normal operation and high-impedance characteristic during a fault on the DC side to limit the fault current rise [10].

Several researchers have conducted extensive studies on current-limiting devices for DC systems. Several strategies have been proposed to solve the DC fault clearance problem. Typically, a DC circuit breaker (DCCB) is used to cut off the faulty line [11]. However, owing to problems with arc extinguishing and insulation technology [12], the increase in maintenance costs caused by the duplication of the interrupting current [13], and increasing metal oxide arrester energy consumption [14,15], it becomes too expensive to solely rely on DCCB to isolate the faulty line of the power grid. Reference [16] proposed a hybrid circuit breaker without load current switching that can reduce the conduction loss during normal operation; however, the rate of fault current rise is significantly fast. Therefore, it is necessary to implement appropriate measures to limit the increase in the fault current before the DCCB operates.

Some scholars have proposed installing smoothing reactors at both ends of the DC line to limit the rate of current increase after a fault. However, the installation of such reactors increases project costs and results in damping characteristics and reduced system stability [17,18]. Therefore, it is crucial to select a suitable fault current limiter for the DC system of an IPFC.

Currently, DC fault current limiters can be categorized into two main groups: superconducting fault current limiters (SFCLs) [19,20,21] and current limiters based on power limiters [22,23]. SFCLs utilize superconducting materials to enhance the line impedance via the quench phenomenon that occurs during a fault to limit the fault current. In [24], a quenching method was proposed for a balanced SFCL using a neutral line to increase the current-limiting rate. However, owing to the difficulty in producing superconducting materials and the high maintenance costs, there are currently few applications in high-voltage DC systems. Power electronics-based current limiters can be further categorized into solid-state fault current limiters (SSFCLs) and hybrid current limiters. SSFCLs have the advantages of a short action time, no arc, no light, and no sound, but they also have the disadvantages of high cost and device loss. Hybrid current limiter combines the advantages of power electronic devices and mechanical switches. References [25,26] present two current limiter topologies for voltage-sourced converter-based high-voltage (VSC-HVDC) faults with parameter design methods and reclosing schemes.

At present, most of the fault current limiter topologies proposed by scholars are aimed at flexible DC power grids, and there is currently no fault current limiter proposed for FACTS equipment, especially the IPFC. The modular multilevel converter-based interline power flow controller (MMC-IPFC) and VSC-HVDC have similar DC structures. When the DC bus is faulty, the discharge mechanism of the MMC submodule is the same. But their operating characteristics are fundamentally different. Existing fault limiters are problematic when used directly in the IPFC. Firstly, the IPFC operates with a bidirectional DC current, so the current limiter needs to have strong bidirectional current capability. In addition, if the fault current reaches the MMC blocking value after the fault, it will cause the IPFC to exit operation. After the IPFC exits, the reactive power of the auxiliary control side of the IPFC will not be controlled, and at the same time, the reactive power and active power of the main control side IPFC will lose control. The existing inductive current limiters still have the limiting inductance connected in series in the circuit when the circuit breaker is activated. This will increase the breaking time of the circuit breaker and the energy consumption of the lightning arrester in the circuit breaker.

Therefore, it is necessary to develop a new type of fault current limiter that is more cost-effective and practical for the IPFC. To solve these problems, this study proposes an FCL topology suitable for DC-side fault ride-through of IPFCs. The novelty of the proposed strategy is as follows.

A DC-side fault current limitation method for the IPFC is proposed for the first time, which can assist with the DC-side fault ride-through of the IPFC and effectively limit the fault current.

The proposed current limiter can limit the fault current below the MMC blocking current and enable IPFC non-blocking fault ride-through, thereby improving the survival capability of the IPFC. After the circuit breaker cuts off the fault, the IPFC can resume normal operation in a short period of time.

The proposed IPFC limiter exhibits low-impedance characteristics in the steady state and low on-state loss, ensuring that the normal operation of the IPFC is not affected.

The proposed current limiter only requires the use of thyristors without the need for expensive fully controlled devices. At the same time, the fault current is limited to a lower level, which can greatly reduce the energy consumption of the lightning arrester in the DC circuit breaker. This will reduce the overall cost.

The remainder of this paper is organized as follows. In Section 2, we present the topology of the proposed current limiter followed by an analysis of its action processes of the current limiter in stages. In Section 3, we examine the influence of the device parameters on the current-limiting effect and provide a parameter selection method. Section 4 presents the pre-charge capacitor charging scheme and fast bypass of the current-limiting inductor. In Section 5, the proposed current limiter is validated in a DC and three-terminal IPFC system and compared with other current-limiting schemes. Finally, Section 6 concludes the paper.

2. Current Limiter Topology and Current-Limiting Process Suitable for IPFC DC Side

2.1. Topology of IPFC

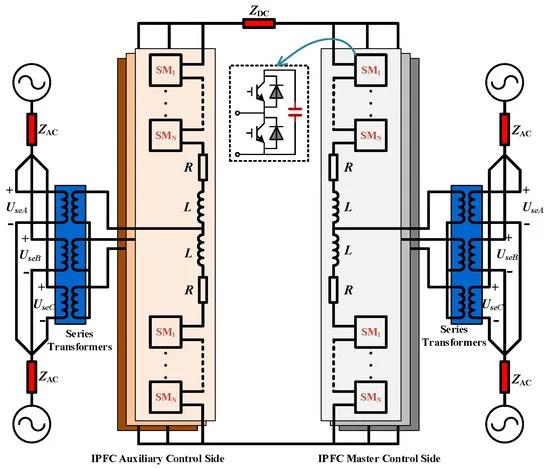

Figure 1 illustrates a two-terminal IPFC system with converter stations connected by series transformers at each terminal of the DC side. The IPFC has at least one auxiliary control side, whose main function is to maintain the DC-side voltage, and at the same time can control the reactive power flow of the line. The IPFC can have multiple master control sides, with an injection voltage Use superimposed on the voltage source by the voltage generated by the inverter at the converter station. As a result, the IPFC can control the active and reactive power flow of multiple lines on the master control sides.

Figure 1. Two-terminal IPFC system.

2.2. DC Fault Vulnerability Analysis

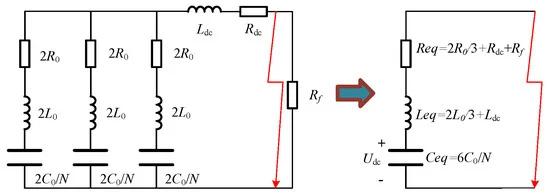

The equivalent circuit diagram of the submodule discharge before blocking the MMC-IPFC converter station after a fault is shown in Figure 2. R0 and L0 denote the equivalent resistance and equivalent inductance in a single bridge arm, respectively; C0 is the capacitance value of a single MMC submodule; and N denotes the number of the submodules in the input state. Rdc and Ldc are the equivalent inductance and resistance of the converter up to the fault point, respectively, and Rf is the fault resistance. As the three-phase units of the MMC are identical and connected in parallel, they can be simplified to an RLC second-order equivalent circuit. The figure shows that due to the small impedance in the circuit after the fault, the fault current rises and the DC voltage drops quickly.

Figure 2. Submodule capacitive discharge equivalent circuit.

2.3. IPFC Fault Current Limiter Topology

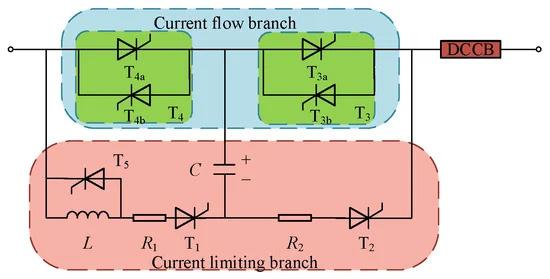

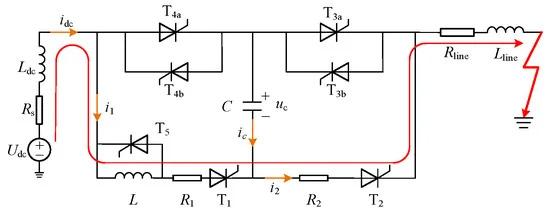

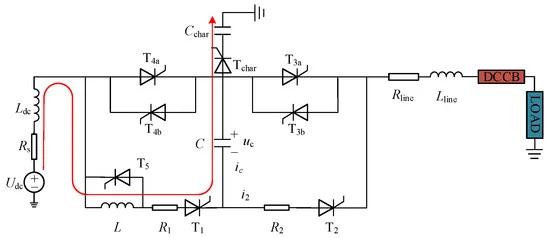

Figure 3 shows the proposed DC fault-current limiter and its connection to the DC circuit breaker. The limiter comprises two main components: the flow branch under normal conditions and the limiter branch. To accommodate the positive and negative currents that occur during the normal operation of the IPFC, the flow branch adopts a structure of two thyristors connected in reverse parallel. The limiter branch comprises three parts: (1) the pre-charge capacitor C, which commutates the fault current to current-limiting path and ensures the reliable shutdown of T3 by pre-charging its voltage; (2) the auxiliary commutation branch comprising auxiliary commutation resistance R2 and thyristor T2, which transfers current from the flow branch to the current-limiting branch and limits the current increase; and (3) the main current-limiting inductor L, current-limiting resistor R1, and thyristors T1 and T5. Inductors L and R1 further suppress the fault current, whereas T5 bypasses inductor L quickly when the circuit breaker operates to reduce the energy consumption of the arrester and the associated costs.

Figure 3. Current limiter topology.

2.4. Action Process and Theoretical Analysis of Current Limiter

2.4.1. Current Limiter Action Process

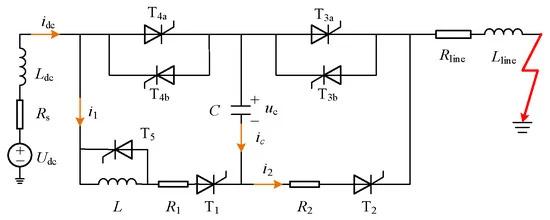

The current limiter was positioned at the outlet of the converter. Assuming that the current flows from left to right, the limiter carries both positive and negative currents during normal operation. In the event of a DC-line fault, the converter station supplies power to the current limiter. When the fault current flows from right to left, it increases rapidly. However, when the fault current flows from left to right, it rapidly decreases to zero and then increases again in the positive direction.

During normal operation, the thyristors T3 and T4 are in a normal trigger state, and the current flows through the current branch as usual.

When a fault occurs, the current rapidly increases. When the current reaches the fault detection condition, T3 and T4 are turned off, and T2 and T1 are turned on. Thyristor T2 conducts under the forward voltage of the capacitor C, and the current is quickly transferred to the auxiliary commutation branch. After the current of thyristor T3a decreases to zero, capacitor C is not discharged completely, and T3a withstands the reverse voltage of capacitor C for a reliable shutdown.

As the voltage of capacitor C drops to zero, the current continues to charge it and thyristor T1 turns on due to the forward voltage, putting the main current-limiting branch into operation. As the current increases, when the sum of the capacitor voltage and resistor R1 voltage exceeds the system voltage, the line current begins to decrease. After T4a current drops to zero, the thyristor is turned off; the voltage across C reaches its maximum value, and the fault current is transferred to the current-limiting branch.

2.4.2. Theoretical Analysis of Current-Limiting Process

Assuming a unipolar ground fault, as shown in Figure 4, occurs on the DC line at time t0, where Ldc represents the current-limiting reactor, RS is the system resistance, and Rline and Lline represent the line impedances as lumped parameters. In this case, the capacitor of the MMC submodule is not considered to be discharged; instead, it is replaced by a DC power supply Udc. At the end of this section, we will present the simulation results applied to IPFC.

Figure 4. DC line fault equivalent circuit.

(1)t0–t1 fault detection stage

During normal operation, the current passes through the flow branch, resulting in minimal loss of the current limiter. However, in the event of a fault, the current increases sharply and continues to flow through the current branch until reaching the DC grid protection and detection device. Figure 5 illustrates the current path during this stage.

Figure 5. t0–t1 fault current path.

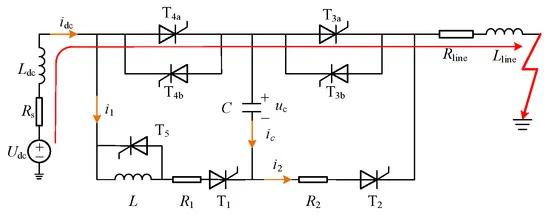

(2) t1–t2 current transfer stage

At time t1, the DC current reaches the fault detection condition, triggering T1 and T2 and signaling T3a and T3b to shut down. Owing to the pre-charged capacitor voltage, T2 can bear the forward voltage and commutate the fault current from the current branch to the auxiliary commutation branch. Further, the pre-charged capacitor voltage is added to both ends of T3a, causing the voltage at both ends to reverse and rapidly decrease the anode current. Additionally, the preset voltage of capacitor C is opposite to the line voltage, which aids in reducing the current on the line and absorbing it to the branch where C is located. After the current decreases to zero, the capacitor remains partially charged, and the voltage at both ends is added to the T3a thyristors to ensure a reliable turn-off. To guarantee a reliable thyristor turn-off, the capacitor discharge time should exceed 100 μs. The current path during this stage is shown in Figure 6.

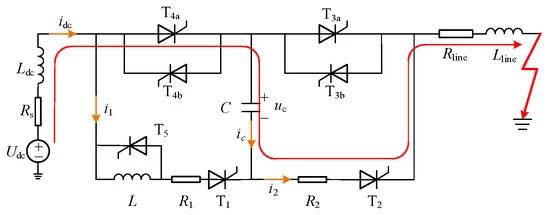

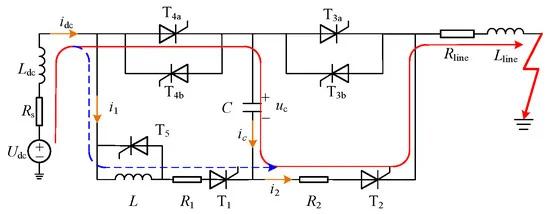

As capacitor C charges, its voltage uc gradually increases. When the sum of uc and the line resistance voltage exceeds the system voltage Udc, the line current begins to decrease. At this point, the voltage across the current-limiting reactor on the line becomes negative on the left and positive on the right. The capacitor continues to charge until the commutation process ends at time t3, when its voltage exceeds the system voltage.

(4)t3–t4 main current-limiting stage

At time t3, the capacitive current ic drops to zero, and the current is completely transferred to the current-limiting branch, fully switching on the current limiter and entering the main current-limiting stage. The current path for this stage is shown in Figure 8.

Figure 8. Fault current path during t3–t4 period.

The dynamic process of the system at this stage can be expressed as:

(13)where Rsum = Rs + R1 + R2 + Rline and Lsum = Ldc + L + Lline. The calculation method for I2 = idc(t3) is as follows. By substituting uc(t2) = 0 into (4), we can obtain the starting time t2 of the capacitor commutation and line current idc(t2) = I1 at that time. Therefore, the initial condition for (11) is given by (14). By substituting (14) and the condition that the capacitive current ic(t3) = 0 into (11) at time t3, we obtain I2.

To further analyze the reliable turn-off of T4a, we need to consider the voltage at both ends of capacitor C at time t2+–t3−. At this time, the voltage is equal to the voltage at both ends of the branch where T1 is located. At time t3, the current in T4a drops to zero and the voltage across the capacitor reaches its maximum value. At time t3+, T4a turns off the capacitive commutation and the process ends. Assuming a negligible line resistance and impedance, we can apply KVL to obtain

From (15), we can obtain:

Equation (16) indicates that based on the previous analysis, uc_max is larger than Udc. Therefore, it can be inferred that uT3a(t3+ < t < t4) < 0, which implies that the T3a thyristors will immediately bear the reverse voltage after the capacitive commutation is completed. They can be turned off reliably after withstanding the reverse voltage for a certain period.

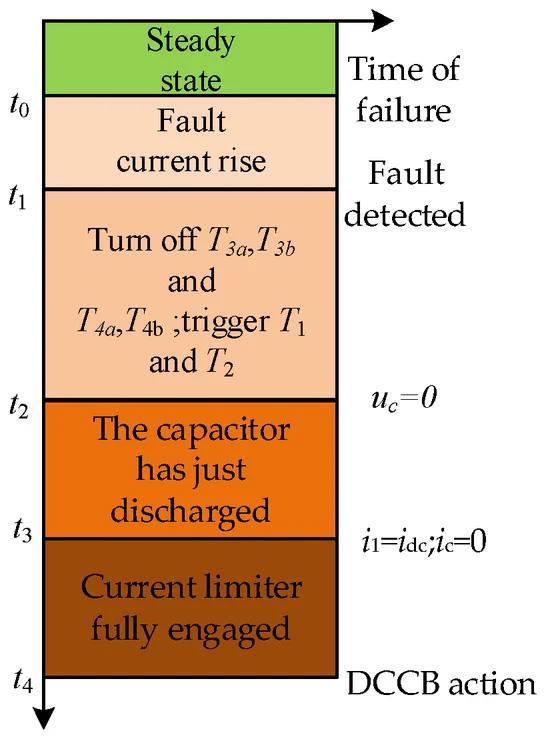

The various time nodes of the current-limiting process are shown in Table 1. Figure 9 shows the control strategies for each stage during the operation of the current limiter.

Figure 9. Fault current limiter control action process.

3. Parameter Design of Current Limiter

For the t1–t2 current transfer stage, it is necessary to ensure that the current is commutated to the auxiliary commutation branch. After the commutation is completed, the thyristor must be reliably turned off; that is, T4a must withstand the reverse voltage for a certain period of time.

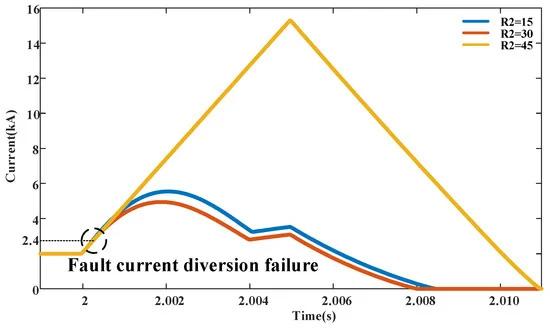

We first consider that the current can be transferred to the auxiliary commutation branch, assuming that the DC line is a 400-kV system with a rated current of In = 2 kA. The system detects that the fault occurs when the DC current is 20% higher than the system rated value, and idc(t1) = 2.4 kA. To ensure successful commutation, the pre-charge capacitor voltage must satisfy (17):

In this study, the pre-charging voltage was set to 100 kV. It can be observed from (17) that when R2 is significantly large, the commutation fails as shown in Figure 10. From Figure 10, we can see that as the resistance R2 increases, the amplitude of the fault current decreases. But when the resistance value increases to a certain extent, the current limiter will fail to perform commutation and lose its current-limiting ability. Therefore, the resistance value of R2 should be less than the value that causes the current limiter to fail commutation. Considering that the function of R2 is to convert the fault current into the limiting current, rather than limit the rise of the fault current, the selected resistance value of R2 does not need to be very large. Therefore, on the basis of considering a certain design margin, economy, and current-limiting effect, we selected a resistor R2 with 20 Ω as the resistance value of the auxiliary commutation resistance.

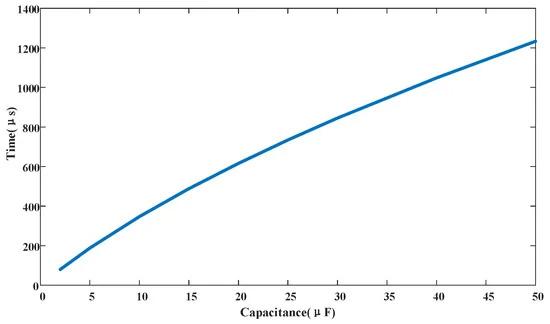

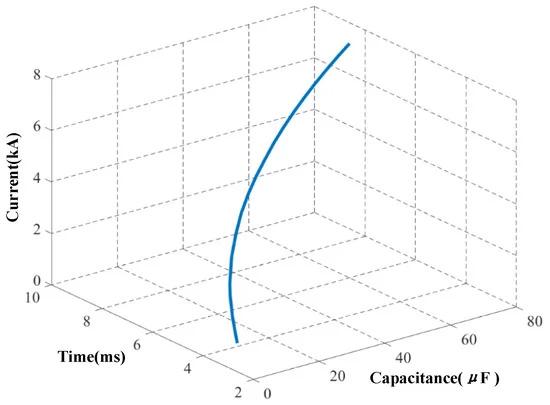

Figure 11 shows the relationship between the size of the pre-charge capacitor and the time used in the current switching stage, where Δt1 = t2 − t1; it can be seen that Δt1, that is, the time for discharging the capacitor, will increase with the increase in capacitance. A capacitor of tens of μF can ensure that the discharge time is more than 100 μs and thyristor T3a is turned off.

The selection of the capacitors should also take into account the system characteristics of the t2–t3 capacitor commutation stage. We first consider the influence of capacitance on the capacitance commutation time Δt2 = t3 − t2 and the idc_max of the maximum current in the commutation process. The smaller the capacitance, the faster the charging speed of the line to the capacitor, and the faster the capacitor voltage rises, which will accelerate the current increase on the T1 branch at this stage, which is conducive to the completion of capacitor commutation; at the same time, it will also reduce idc to decrease the value of idc_max. The relationship between the value of C and Δt2 and idc_max is shown in Figure 12, and the results are consistent with the above inference.

Figure 12. Relationship between C, Δt2, and idc_max.

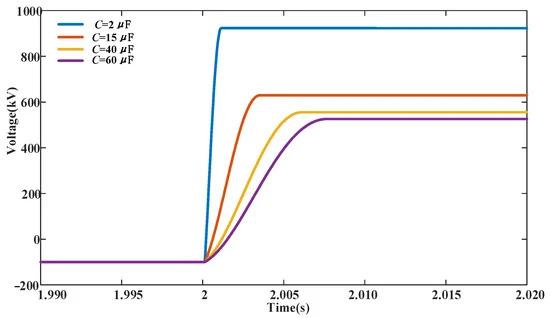

However, considering the capacitor voltage after the capacitor is charged, it is easy to know from the analysis that the smaller the capacitor, the more obvious the charging effect, and the higher the voltage across the capacitor after commutation is completed. Figure 13 shows the voltage change for different capacitance values during the current-limiting process, which proves the correctness of the above inference.

Figure 13. Voltage variations for different commutation capacitors.

For the parameter selection of commutation capacitor C, the first consideration should be to ensure the reliable shutdown of the thyristor T3a. Otherwise, the fault current will still flow through the current branch, and the current limiter will lose its current-limiting ability. From Figure 11, it can be seen that Δt1 increases with the increase in capacitance value. On the basis of considering twice the threshold, capacitance exceeding 5 μF can ensure reliable turnoff of the thyristor. In addition, commutation capacitors can also affect the fault current and the magnitude of Δt2. From Figure 12, it can be seen that as the capacitance value increases, the values of Δt2 and idc_max will both increase. To ensure that MMC does not lock during fault, idc_max should be limited to below 6 kA. Figure 13 also shows the variation in commutation capacitor voltage with the change in capacitance value. A too-small capacitance value can cause the capacitance voltage to be too high, causing more insulation problems for the components. Considering the above reasons, the commutation capacitance was taken as 20 μF.

4. Pre-Charge Capacitor Charging Scheme and Current-Limiting Inductor Fast Bypass Technology

4.1. Pre-Charging Capacitor Charging Scheme

Currently, for high-voltage capacitor charging in DC systems, external DC/DC converters and laser energy delivery are generally used. These systems require additional large investments, and at the same time, cause significant security and control problems. In this study, a topological structure was added to charge the capacitors. The charging method is illustrated in Figure 14, where Tchar is the switch of the pre-charging circuit; Cchar is the variable capacitor, whose purpose is to control the pre-charging voltage of the commutation capacitor; and the R1 resistor in the charging circuit can limit the charging current. This method utilizes the existing system structure to charge the commutation capacitor, and can monitor the voltage of the capacitor while the system is running to ensure that the voltage is maintained at a normal level.

Figure 14. Capacitor charging scheme.

4.2. Current-Limiting Inductor Fast Bypass Technology

4.2.1. Inductive Fast Bypass Method

The DC current limiter curbs the escalation of the fault current following a fault and provides a window for fault detection. Once a faulty line is identified, the DC circuit breaker on the line can interrupt the fault current.

Considering the ABB hybrid DCCB as an example, the arrester kicks in and consumes energy immediately after the operation of the main circuit breaker, causing the line fault current to drop instantaneously. However, in the current limiter scheme outlined in this paper, the main current-limiting inductance L remains connected in series with the faulty circuit even after the circuit breaker is tripped, thereby hindering the attenuation of the fault current. To address this issue, this paper proposes the use of current-limiting inductance fast-bypass technology, which bypasses the current-limiting inductance L once the circuit breaker operates, effectively removing it from a faulty circuit. This reduced the cutoff time of the circuit breaker and the energy absorbed by the arrester. After the fault is cleared, the pre-charged capacitor is activated, forming an energy transfer loop that eventually dissipates the energy stored in the inductor. The specific process is described below.

(1)Once the system experiences failure, the current limiter is activated in the fault circuit using the sequence of actions outlined in the previous section. This is repeated until the capacitor commutation current limiter was completely operational. Further refinement of the system may be required to ensure optimal performance in the event of future failure.

(2)Fast bypass of current-limiting inductor.

When a fault is detected by the system protection mechanism, the IGBT in the DCCB transfer branch is deactivated, causing the arrester to begin consuming energy, resulting in a rapid decrease in the fault current. At this point, the voltage across the current-limiting inductor suddenly becomes negative on the left and positive on the right. When T5 is triggered, the inductance L is bypassed and the current in L remains constant while the energy is temporarily stored in the loop. Because of the arrester, the fault circuit current continues to decrease until it reaches the operational value of the isolation switch, at which point the switch is triggered and the fault is fully removed from the line. Further system improvements may be required to optimize the performance in the event of future faults.

(3)Energy consumption of current-limiting inductor.

Once the fault has been cleared, the inductance L retains 0.5LI32 of the magnetic field energy, and a circulating current is formed with T5. This current must be consumed, and the following method is used. After the fault is cleared, T4b and T1 are triggered, and the voltage across capacitor C is added to both ends of T5, causing it to shut off owing to the reverse voltage. The current then flows through L, T1, C, and T4b to form a loop. The current in the inductor gradually decreases to zero. As L is a 100 millihenry inductance and C is a ten-microfarad capacitor, the voltage across the capacitor returns to the lower positive and upper negative polarities after the discharge of L is complete. At this point, because of the thyristor in the loop, the capacitor no longer discharges, and the energy in the inductor is transferred to the capacitor along with a portion of the energy consumed by resistor R1. T2 and T3b are triggered again, and the remaining energy in the capacitor is consumed by resistor R2. Further refinement may be necessary to ensure optimal system performance.

4.2.2. Approximate Calculation of Arrester Energy Consumption Reduction

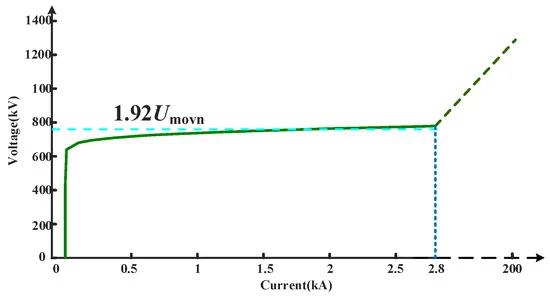

At time t4, the transfer branch IGBT in the DCCB is controlled to turn off, and the arrester begins to consume energy, assuming that the line current drops to zero at time t5. This period was calculated as Δt3 = t5 − t4. To calculate the effect of the current-limiting inductor fast bypass on the energy consumption of the arrester, it was necessary to simplify its working characteristics. Figure 15 shows the I–V characteristic curve of the arrester, where V is the unit value of the terminal voltage of the arrester, and its reference value is the rated voltage Umovn of the arrester. When the current flowing through the arrester changes, the voltage at both ends also changes; however, at a current of several kiloamperes, the voltage value can be approximated as kUmovn, where k is a constant. In this study, k was set as 1.92. To ensure a complete representation of the I–V curve, the portion of the graph where the current exceeds 2.8 kA is shown as a dashed line.

5. Model Validation

5.1. DC System Verification

This section validates the current-limiting method previously discussed for single-ended DC systems. Theoretical and simulation results were compared to confirm the accuracy of the analysis of the current limiter action process. Additionally, the bypass effect of the current-limiting inductor was demonstrated.

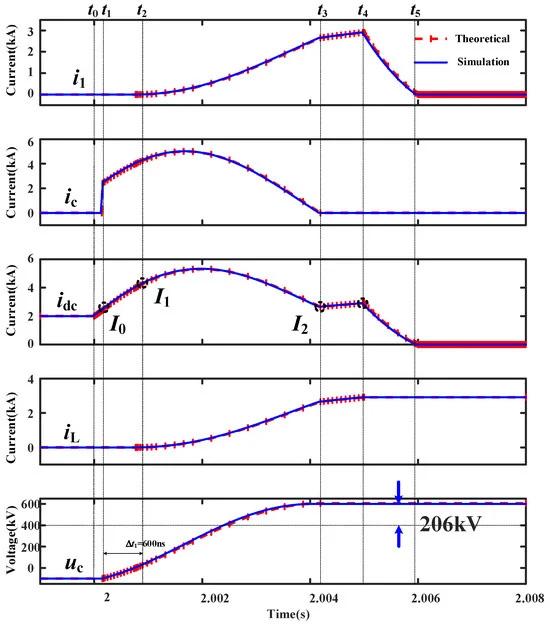

The simulation system is illustrated in Figure 16. The rated DC voltage of the system is Udc = 400 kV, the rated DC current is In = 2 kA, and the current-limiting reactor is Ldc = 0.15 H, ignoring the system internal resistance and current-limiting impedance. The parameters of the current limiter are as follows: L = 0.4 H, R1 = 60 Ω, R2 = 20 Ω, C = 20 μF, and the capacitor pre-charge voltage U0 = 100 kV; the I–V curve of the arrester is shown in Figure 15, and the rated voltage is 400 kV. At t = 2.0 s, a unipolar ground fault occurs in the system. When the current exceeds the rated value by 20%, the current limiter is activated. The action of the current limiter is described above. The key parameters of the current-limiting process are shown in Figure 16. In the figure, the simulation results are represented by solid lines, and the numerical calculation results are represented by dotted lines.

Figure 16. Comparison of theoretical calculation results and simulation results in the current-limiting process.

It can be seen from Figure 16 that the theoretical numerical calculation results are relatively close to the model simulation results, which proves the correctness of the state analysis in each time period after the current limiter is activated, as described in the Section 2 of this paper. It can be seen from the figure that the capacitor voltage uc is the voltage across the thyristor T3a in the current commutation stage, and the time required for this stage is Δt1 = 600 ns, which can ensure the reliable shutdown of the thyristor. After the current limiter is fully engaged, uc becomes higher than the system voltage by 206 kV, which can ensure that the voltage at both ends of T4a is negative on the left and positive on the right, ensuring its reliable shutdown. The analysis of the above two points proves the rationality of the parameter selection analysis described in the Section 3 of this paper.

In Figure 16, the third figure corresponds to the derivation of the idc value in the Section 2. From the figure, it can be seen that the calculated values of the fault current I0, I1, I2 at each time node proposed in Section 2 have a small error compared to the simulation values. Therefore, it is reasonable to use the mathematical model in Section 2 for the selection of component parameters in Section

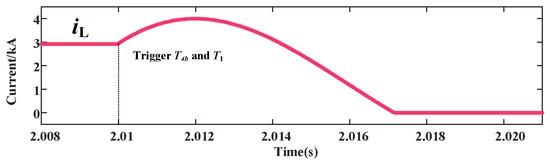

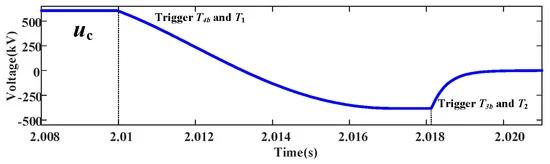

3.Next, we analyzed the consumption of energy stored in the current-limiting inductance L due to the bypass after the circuit breaker operates. As shown in Figure 16, the circuit breaker operates at t = 2.005 s; the inductor current remains unchanged due to the withdrawal of the fault circuit iL by the fast bypass, and the capacitance uc also remains unchanged. Figure 17 and Figure 18 show the changes in the inductor current and capacitor voltage during inductor energy transfer and consumption after the circuit breaker operates. Then, T4b and T1 are triggered at time t6. As iL and uc are in the same direction, the current first increases. After the capacitor discharge ends, the inductor charges the capacitor, and the current decreases. Finally, all the energy in the inductor is transferred to the capacitor, and the capacitor voltage becomes positive at the bottom and negative at the top. T2 and T3b are triggered at t7; the energy in the capacitor is consumed by R2 and its voltage drops to zero. This process is the same as that in the analysis in the Section 4, which proves the correctness of the theoretical analysis.

Figure 17. Current through the current-limited inductor.

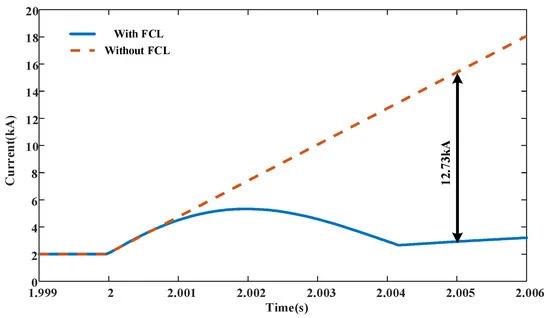

Figure 19. Comparison of current-limiting effect.

Figure 20 compares the line currents in the two cases in which the current-limiting inductor in the current limiter is bypassed after the DCCB action. It can be seen that if the inductor is still in the loop when the DCCB operates, the DCCB disconnection time is 3.6 ms. After the current-limiting inductor is bypassed, the DCCB disconnection time is 1 ms; that is, the current-limiting inductor bypass technology can reduce the disconnection time by 2.6 ms. Figure 21 compares three control strategies after a fault occurs: (1) the current limiter does not operate; (2) the current limiter operates but the inductor does not bypass; (3) the current limiter operates and the inductor is bypassed. In these three cases, it can be seen that the investment in the current limiter and the application of the current-limiting inductance bypass technology can significantly reduce the energy consumption of the arrester when the DCCB operates and also reduce the cost of the arrester.